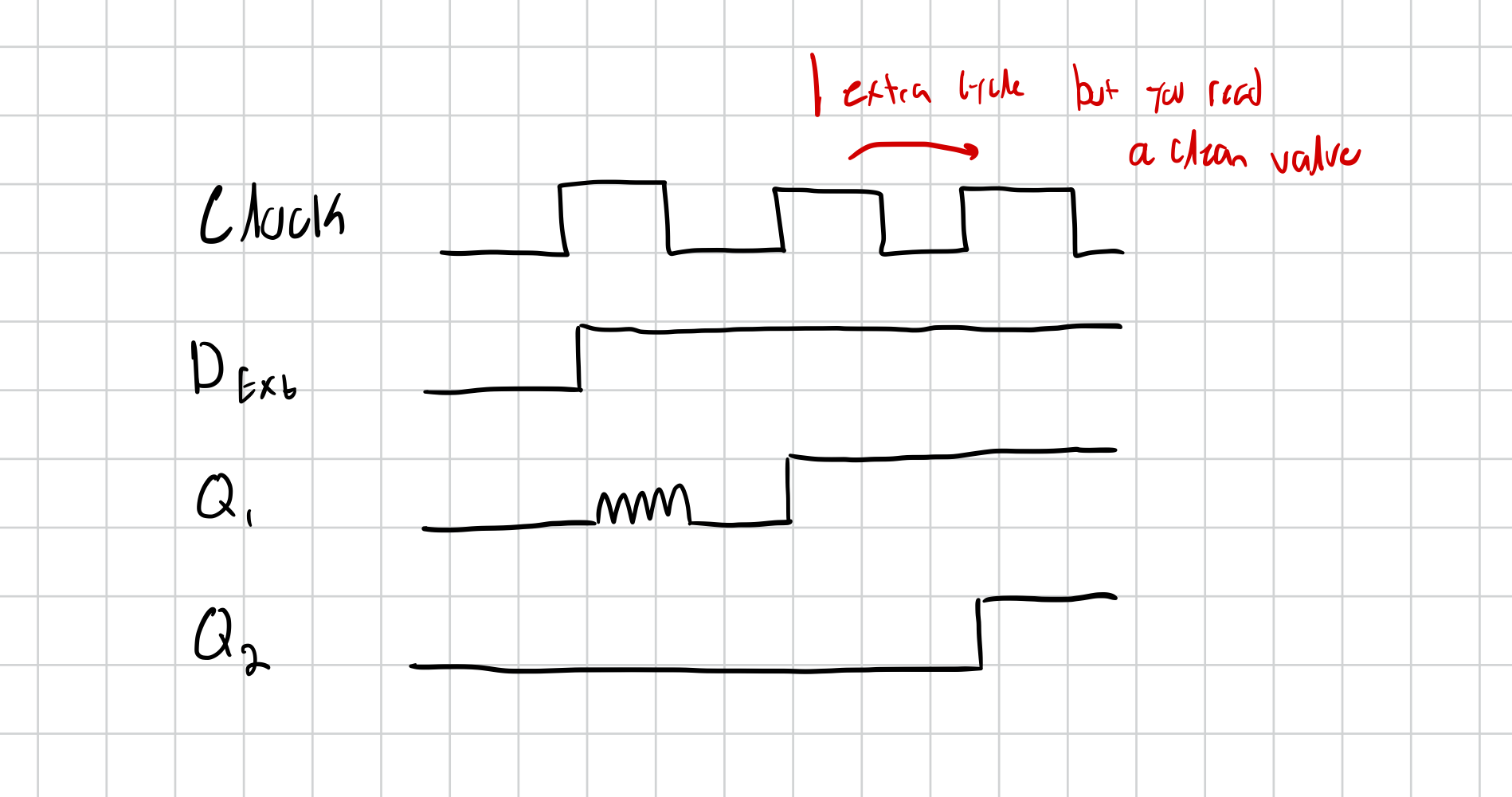

This is what happens when you violate the setup or hold times of a flip flop.

D Flip Flop

Basically, Input = Output on the rising edge of a clock

Issues arise when you try to set and reset at the same time (if you set and reset too close to each other within the magnitude of nano to pico seconds due to gate delays)

Mitigating Metastability

You can just stick another D flip flop after the first one

If you read in an oscillating value, it takes an additional clock cycle to read a clean value, but that value will be read