Similar to a Synchronous Bus Read

Timing

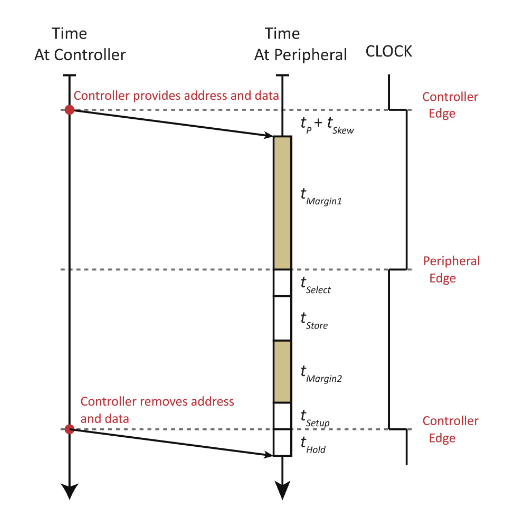

After sending the address and data, everything happens from the peripherals view of time

Flow

- Send address and data from controller to peripheral

- Wait for propagation and skew time

- Wait for margin time (falling edge)

- Wait for the select, store (after device is selected, get everything ready to be stored but don’t actually store) and margin time (margin time aligns actual storage right at the end of the transaction on the next rising edge)

- Before the next rising edge, wait for setup time (actually stores the data)

- On rising edge, start hold time (where hold time is 0 ideally)

- The controller removes the address and data from the peripheral (on next rising edge but occurs after setup and hold time)

The normal clock and register clock are inverted from each other…

Why?

- To minimize skew time?

- On the falling edge of the normal clock, the register clock goes high because data is ready and the register can do things?

Clock expressions

Normal Clock

Register Clock (this gets you a write lined up with a rising clock edge)